# TSL: A System for Generating Abstract Interpreters and its Application to Machine-Code Analysis

JUNGHEE LIM

University of Wisconsin

and

THOMAS REPS

University of Wisconsin and GrammaTech, Inc.

This paper describes the design and implementation of a system, called TSL (for "Transformer Specification Language"), that provides a systematic solution to the problem of creating retargetable tools for analyzing machine code. TSL is a tool generator—i.e., a meta-tool—that automatically creates different abstract interpreters for machine-code instruction sets.

The most challenging technical issue that we faced in designing TSL was how to automate the generation of the set of abstract transformers for a given abstract interpretation of a given instruction set. From a description of the concrete operational semantics of an instruction set, together with the datatypes and operations that define an abstract domain, TSL automatically creates the set of abstract transformers for the instructions of the instruction set. TSL advances the state of the art in program analysis because it provides two dimensions of parameterizability: (i) a given analysis component can be retargeted to different instruction sets; (ii) multiple analysis components can be created automatically from a single specification of the concrete operational semantics of the language to be analyzed.

TSL is an abstract-transformer-generator generator. The paper describes the principles behind TSL, and discusses how one uses TSL to develop different abstract interpreters.

Categories and Subject Descriptors: D.2.4 [Software Engineering]: Software/Program Verification—Assertion checkers; model checking; D.2.5 [Software Engineering]: Testing and Debugging—Symbolic execution; testing tools; D.2.7 [Software Engineering]: Distribution, Maintenance, and Enhancement—Restructuring, reverse engineering, and reengineering; D.3.2 [Programming Languages]: Language Classifications—Applicative (functional) languages; macro and assembly languages; F.3.2 [Logics and Meanings of Programs]: Semantics of Programming Languages—Program analysis

Authors' addresses: J. Lim, Computer Sciences Dept., Univ. of Wisconsin, 1210 W. Dayton St., Madison, WI 53703, junghee@cs.wisc.edu. T. Reps, Computer Sciences Dept., Univ. of Wisconsin, 1210 W. Dayton St., Madison, WI 53703, and GrammaTech, Inc., 531 Esty St., Ithaca, NY 14850; reps@cs.wisc.edu.

The work was supported in part by NSF under grants CCF-{0524051, 0540955, 0810053, 0904371}; by ONR under grants N00014-{01-1-0708, 01-1-0796, 09-1-0510, 09-1-0776, 10-M-0251, 11-C-0447}; by ARL under grant W911NF-09-1-0413; by AFRL under grants FA8750-05-C-0179, FA8750-06-C-0249, FA9550-09-1-0279 and FA8650-10-C-7088; by DARPA under cooperative agreement HR0011-12-2-0012; by a donation from GrammaTech, Inc.; and by a Symantec Research Labs Graduate Fellowship. Any opinions, findings, and conclusions or recommendations expressed in this publication are those of the authors, and do not necessarily reflect the views of the sponsoring companies or agencies.

T. Reps has an ownership interest in GrammaTech, Inc., which has licensed elements of the technology reported in this publication.

Portions of this work appeared in the 17th Int. Conf. on Compiler Construction [Lim and Reps 2008], the 16th Int. SPIN Workshop [Lim et al. 2009] and a subsequent journal article [Lim et al. 2011], and the 22nd Int. Conf. on Computer Aided Verification [Thakur et al. 2010], as well as in J. Lim's Ph.D. dissertation [Lim 2011].

© 2012 J. Lim and T. Reps

General Terms: Algorithms, Languages, Security, Theory, Verification Additional Key Words and Phrases: Abstract interpretation, machine-code analysis, dynamic analysis, symbolic analysis, static analysis, dataflow analysis

## 1. INTRODUCTION

In recent years, methods to analyze machine-code programs have been receiving increased attention. Two of the factors that motivate such work are (i) source code is often unavailable, and (ii) machine code is closer than source code to what is actually executed, which is often important in the context of computer security. While the tools and techniques that have been developed for analyzing machine code are, in principle, language-independent, implementations are often tied to one specific instruction set. Retargeting them to another instruction set can be an expensive and error-prone process.

This paper describes the design and implementation of a system, called TSL (for "Transformer Specification Language"), that provides a systematic solution to the problem of creating retargetable tools for analyzing machine code. TSL is a tool generator—i.e., a meta-tool—that automatically creates different abstract interpreters for machine-code instruction sets. More precisely, TSL is an abstract-transformer-generator generator. The TSL system provides a language in which a user specifies the concrete operational semantics of an instruction set; from a TSL specification, the TSL compiler generates an intermediate representation that allows the meanings of the input-language constructs to be redefined by supplying alternative interpretations of the primitives of the TSL language (i.e., the TSL base-types, map-types, and operations on values of those types). TSL's run-time system supports the use of such generated abstract-transformer generators for dynamic analysis, static analysis, and symbolic execution.

TSL advances the state of the art in program analysis by providing a YACC-like mechanism for creating the key components of machine-code analyzers: from a description of the concrete operational semantics of a given instruction set, TSL automatically creates *implementations* of different abstract interpreters for the instruction set.

In designing the TSL system, the most challenging technical issue that we faced was how to automate the generation of the set of abstract transformers for a given abstract interpretation of a given instruction set. There have been a number of past efforts to create generator tools to support abstract interpretation, including MUG2 [Wilhelm 1981], SPARE [Venkatesh 1989; Venkatesh and Fischer 1992], Steffen's work on harnessing model checking for dataflow analysis [Steffen 1991; 1993], Sharlit [Tjiang and Hennessy 1992], Z [Yi and Harrison, III 1993], PAG [Alt and Martin 1995], OPTIMIX [Assmann 2000], TVLA [Lev-Ami and Sagiv 2000; Reps et al. 2010], HOIST [Regehr and Reid 2004], and RHODIUM [Scherpelz et al. 2007]. However, in all but the last three, the user specifies an abstract semantics, but not the concrete semantics of the language to be analyzed. Moreover, it is the responsibility of the user to establish, outside of the system, the soundness of

<sup>&</sup>lt;sup>1</sup>TSL is also used as the name of the system's meta-language.

the abstract semantics with respect to the (generally not-written-down) concrete semantics.

In contrast, a major goal of our work was to adhere closely to the credo of abstract interpretation [Cousot and Cousot 1977]:

- —specify the concrete semantics

- —obtain an abstract semantics as an abstraction of the concrete semantics.

In particular, a specification of the concrete semantics of the language to be analyzed is an explicit artifact that the TSL compiler receives as input. Consequently, TSL differs from most past work that has attempted to automate the creation of abstract interpreters.

A language's concrete semantics is specified in TSL's meta-language. The meta-language is a strongly typed, first-order functional language with a datatype-definition mechanism for defining recursive datatypes, plus deconstruction by means of pattern matching. Thus, writing a TSL specification for an language is similar to writing an interpreter for that language in first-order ML.

TSL provides a fixed set of basetypes and operators, as well as map-types with map-access and (applicative) map-update operations. From a TSL specification, the TSL compiler generates a common intermediate representation (CIR) that allows the meanings of the input-language constructs to be redefined by supplying alternative interpretations of the basetypes, map-types, and the operations on them (also known as "semantic reinterpretation"). Because all the abstract operations are defined at the meta-level, semantic reinterpretation is independent of any given language defined in TSL. Therefore, each implementation of an analysis component's driver serves as the unchanging driver for use in different instantiations of the analysis component to different languages. The TSL language becomes the specification language for retargeting that analysis component for different languages. Thus, to create  $M \times N$  analysis components, the TSL system only requires M specifications of the concrete semantics of a language, and N analysis implementations, i.e., M + N inputs to obtain  $M \times N$  analysis-component implementations.

*Problem Statement.* Our work addresses the following fundamental problem in abstract interpretation:

Given the concrete semantics for a language, how can one systematically create the associated abstract transformers?

In addition to the theory of abstract interpretation itself [Cousot and Cousot 1977], the inspiration for our work is two-fold:

- —Prior work on systems that generate analyzers from the concrete semantics of a language: TVLA, HOIST, and RHODIUM.

- —Prior work on semantic reinterpretation [Mycroft and Jones 1985; Jones and Mycroft 1986; Nielson 1989; Malmkjær 1993].

The use of semantic reinterpretation in TSL as the basis for generating abstract transformers is what distinguishes our work from TVLA, HOIST, and RHODIUM. Semantic reinterpretation is discussed in more detail in §2.2 and §3.2.

Our work also addresses the *retargeting problem*. The literature on program analysis is vast, and essentially all of the results described in the literature are, in principle, language-independent. However, their implementations are often tied to one specific language. Retargeting them to another language (as well as implementing a new analysis for the same language) can be an expensive and error-prone process. TSL represents one point in the design space of tools to support retargetable program analyzers, namely, a meta-tool—a tool generator—that automatically creates different abstract interpreters for a language.

Contributions. TSL advances the state of the art in program analysis because it provides two dimensions of parameterizability. In particular,

- —a given analysis component can be retargeted to different instruction sets. One merely has to write a TSL specification of the concrete semantics of a given instruction set. In this respect, TSL provides a YACC-like mechanism for creating different instantiations of an analysis component for different languages: from a description of the concrete operational semantics, TSL automatically creates implementations of different analysis components.

- —multiple analysis components can be created automatically from a single specification of the concrete operational semantics of the language to be analyzed. For each new analysis component, the analysis designer merely has to provide a reinterpretation of the basetypes, map-types, and operators of the TSL metalanguage.

Other notable aspects of our work include

- —Support for multiple analysis types. The system supports several analysis types:

- —classical worklist-based value-propagation analyses

- —transformer-composition-based analyses [Cousot and Cousot 1979; Sharir and Pnueli 1981], which are particularly useful for context-sensitive interprocedural analysis, and for relational analyses

- —unification-based analyses for flow-insensitive interprocedural analysis

- —dynamic analyses (including concrete emulation using concrete semantics)

- —symbolic analyses

- —Implemented analyses. These mechanisms have been instantiated for a number of specific analyses that are useful for analyzing machine code, including value-set analysis [Balakrishnan 2007; Balakrishnan and Reps 2004] (§4.1.1), affine-relation analysis [Müller-Olm and Seidl 2005; Elder et al. 2011] (§4.1.2), def-use analysis (for memory, registers, and flags) (§4.1.4), aggregate structure identification [Ramalingam et al. 1999] (§4.1.3), and generation of symbolic expressions for an instruction's semantics (§4.1.5).

Using TSL, we also developed a novel way of applying semantic reinterpretation to create symbolic-analysis primitives automatically for symbolic evaluation, preimage computation, and symbolic composition [Lim et al. 2011].

—Established applicability. The capabilities of our approach have been demonstrated by writing specifications for IA32 and PowerPC. These are nearly complete specifications of the integer subset of these languages, and include such features as (1) aliasing among 8-, 16-, and 32-bit registers, e.g., al, ah, ax, and

eax (for IA32), (2) endianness, (3) issues arising due to bounded-word-size arithmetic (overflow/underflow, carry/borrow, shifting, rotation, etc.), and (4) setting of condition codes (and their subsequent interpretation at jump instructions). We have also experimented with sufficiently complex features of other machine-code languages (e.g., register windows for Sun SPARC and conditional execution of instructions for ARM) to know that they fit our specification and implementation models.

TSL has been used to recreate the analysis components employed by CodeSurfer/x86 [Balakrishnan et al. 2005], which is a static-analysis framework for analyzing stripped x86 executables. The TSL-generated analysis components include value-set analysis, affine-relation analysis, def-use analysis (for memory, registers, and flags), and aggregate structure identification. From the TSL specification of PowerPC, we also generated the analysis components needed for a PowerPC version, CodeSurfer/ppc32.

In addition, using TSL-generated primitives for symbolic analysis, we developed a machine-code verification tool, called MCVETO [Thakur et al. 2010] (§4.3), and a concolic-execution-based program-exploration tool, called BCE [Lim and Reps 2010] (§4.4).

—Evaluation of the benefits of the approach. As discussed in §5, TSL provides benefits from several standpoints, including (i) development time, and (ii) the precision of TSL-generated abstract transformers.

Organization of the Paper. The remainder of the paper is organized as follows. §2 presents an overview of the TSL system, the principles that lie behind it, and the kinds of applications to which it has been applied. §3 describes TSL in more detail, and considered from three perspectives: (i) how to write a TSL specification (from the point of view of instruction-set-specification developers), (ii) how to write domains for (re)interpreting the TSL basetypes and map-types (from the point of view of reinterpretation developers), and (iii) how to use TSL-generated abstract transformers (from the point of view of tool developers). §4 summarizes some of the analyses that have been written using TSL. §5 presents an evaluation of the costs and benefits of the TSL approach. §6 discusses related work. §7 concludes.

## OVERVIEW OF THE TSL SYSTEM

The goal of TSL is to provide a systematic way of implementing analyzers that work on machine code. TSL has three classes of users: (i) instruction-set-specification (ISS) developers, (ii) reinterpretation developers, and (iii) tool developers. The ISS developers are involved in specifying the semantics of different instruction sets; the reinterpretation developers are involved in defining abstract domains and reinterpretations for the TSL basetypes; the tool developers are involved in extending the analysis framework. The TSL language allows ISS developers to specify the concrete semantics of an instruction set. The TSL run-time system—defined by a collection of C++ classes—allows analysis developers to easily create analyzers that support dynamic analysis, static analysis, and symbolic analysis of executables written in any instruction set for which a TSL semantic specification has been written.

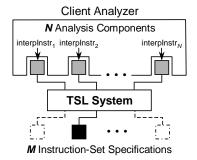

Fig. 1. The interaction between the TSL system and a client analysis tool. Each gray box represents a TSL-generated abstract-transformer generator.

## 2.1 Design Principles

In designing the TSL language, we were guided by the following principles:

- —There should be a formal language for specifying the semantics of the language to be analyzed. Moreover, an ISS developer should specify only the abstract syntax and a concrete operational semantics of the language to be analyzed. Each analyzer should be generated automatically from this specification.

- —Concrete syntactic issues—including (i) decoding (machine code to abstract syntax), (ii) encoding (abstract syntax to machine code), (iii) parsing assembly (assembly code to abstract syntax), and (iv) assembly pretty-printing (abstract syntax to assembly code)—should be handled separately from the abstract syntax and concrete semantics.<sup>2</sup>

- —There should be a clean interface for reinterpretation developers to specify the abstract semantics for each analysis. An abstract semantics consists of an *interpretation*: an abstract domain and a set of abstract operators (i.e., for the operations of TSL).

- —The abstract semantics for each analysis should be separated from the languages to be analyzed so that one does not need to specify multiple versions of an abstract semantics for multiple languages.

Each of these objectives has been achieved in the TSL system: The TSL system translates the TSL specification of each instruction set to a common intermediate representation (CIR) that can be used to create multiple analyzers (§2.3 and §3.1.3). Each analyzer is specified at the level of the meta-language (i.e., by reinterpreting the operations of TSL), which—by extension to TSL expressions and functions—provides the desired reinterpretation of the instructions of an instruction set.

$<sup>^2\</sup>mathrm{The}$  translation of the concrete syntaxes to and from abstract syntax is handled by a generator tool, called ISAL, which is separate from TSL and will not be discussed in this paper. It suffices to say that the relationship between ISAL and TSL is similar to that between Flex and Bison. With Flex and Bison, the specification of a collection of token identifiers is shared, which allows a Flex-generated lexer to pass tokens to a Bison-generated parser. With ISAL and TSL, the specification of an instruction set's abstract syntax is shared, which allows ISAL to pass abstract-syntax trees to a TSL-generated instruction-set analyzer.

```

s_1: x = x \oplus y;

s_2: y = x \oplus y;

s_3: x = x \oplus y;

```

Fig. 2. Code fragment that swaps two ints, using three  $\oplus$  operations.

Many for the Price of One!. In Fig. 1, once one has the N analysis implementations that are the core of some client analysis tool A, one obtains a generator that can create different versions  $A/M_1$ ,  $A/M_2$ , ... at the cost of writing specifications of the concrete semantics of instruction sets  $M_1$ ,  $M_2$ , etc. Thus, each client analysis tool A built using abstract-transformer generators created via TSL acts as a "YACC-like" tool for generating different versions of A automatically.

## 2.2 Semantic Reinterpretation

The TSL system is based on factoring the concrete semantics of a language into two parts: (i) a *client* specification, and (ii) a semantic *core*. The interface to the core consists of certain basetypes, map-types, and operators (sometimes called a *semantic algebra* [Schmidt 1986]), and the client is expressed in terms of this interface. This organization permits the core to be *reinterpreted* to produce an alternative semantics for the *subject language*.<sup>3</sup>

Semantic Reinterpretation for Abstract Interpretation. The idea of exploiting such a factoring comes from the field of abstract interpretation [Cousot and Cousot 1977], where factoring-plus-reinterpretation has been proposed as a convenient tool for formulating abstract interpretations and proving them to be sound [Mycroft and Jones 1985; Jones and Mycroft 1986; Nielson 1989; Malmkjær 1993]. In particular, soundness of the *entire* abstract semantics can be established via purely *local* soundness arguments for each of the reinterpreted operators.

The following example shows the basic principles of semantic reinterpretation in the context of abstract interpretation. We use a simple language of assignments, and define the concrete semantics and an abstract sign-analysis semantics via semantic reinterpretation.

EXAMPLE 2.1. (Adapted from [Malmkjær 1993].) Consider the following fragment of a denotational semantics, which defines the meaning of assignment statements over variables that hold signed 32-bit int values (where  $\oplus$  denotes exclusive-

<sup>&</sup>lt;sup>3</sup>Semantic reinterpretation is a program-generation technique, and thus we follow the terminology of the partial-evaluation literature [Jones et al. 1993], where the program on which the partial evaluator operates is called the *subject program*.

In logic and linguistics, the programming language would be called the "object language". In the compiler literature, an object program is a machine-code program produced by a compiler, and so we avoid using the term "object programs" for the programs that TSL operates on.

$$\begin{split} I \in Id & E \in Expr ::= I \mid E_1 \oplus E_2 \mid \dots \\ S \in Stmt ::= I = E; & \sigma \in State = Id \to Int32 \\ \mathcal{E} : Expr \to State \to Int32 \\ \mathcal{E} \llbracket I \rrbracket \sigma = \sigma I \\ \mathcal{E} \llbracket E_1 \oplus E_2 \rrbracket \sigma = \mathcal{E} \llbracket E_1 \rrbracket \sigma \oplus \mathcal{E} \llbracket E_2 \rrbracket \sigma \\ \mathcal{I} : Stmt \to State \to State \\ \mathcal{I} \llbracket I = E : \rrbracket \sigma = \sigma [I \mapsto \mathcal{E} \llbracket E \rrbracket \sigma] \end{split}$$

By " $\sigma[I \mapsto v]$ ," we mean the function that acts like  $\sigma$  except that argument I is mapped to v. The specification given above can be factored into client and core specifications by introducing a domain Val, as well as operators xor, lookup, and store. The client specification is defined by

$$\begin{aligned} &xor \colon Val \to Val \\ &lookup \colon State \to Id \to Val \\ &store \colon State \to Id \to Val \to State \\ &\mathcal{E} \colon Expr \to State \to Val \\ &\mathcal{E}[\![I]\!]\sigma = lookup \ \sigma \ I \\ &\mathcal{E}[\![E_1 \oplus E_2]\!]\sigma = \mathcal{E}[\![E_1]\!]\sigma \ xor \ \mathcal{E}[\![E_2]\!]\sigma \\ &\mathcal{I} \colon Stmt \to State \to State \\ &\mathcal{I}[\![I]\!] = E; |\![I]\!]\sigma = store \ \sigma \ I \ \mathcal{E}[\![E]\!]\sigma \end{aligned}$$

For the concrete (or "standard") semantics, the semantic core is defined by

$$v \in Val_{std} = Int32$$

$$State_{std} = Id \rightarrow Val$$

$$lookup_{std} = \lambda \sigma.\lambda I.\sigma I$$

$$store_{std} = \lambda \sigma.\lambda I.\lambda v.\sigma [I \mapsto v]$$

$$xor_{std} = \lambda v_1.\lambda v_2.v_1 \oplus v_2$$

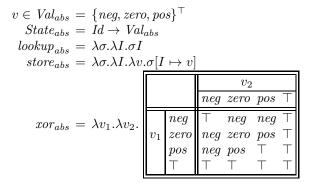

Different abstract interpretations can be defined by using the same client semantics, but giving different interpretations to the basetypes, map-types, and operators of the core. For example, for sign analysis, assuming that Int32 values are represented in two's-complement notation, the semantic core is reinterpreted as follows:

For numbers represented in two's-complement notation,  $pos\ xor_{abs}\ neg = neg\ xor_{abs}\ pos = neg$  because, for all combinations of values represented by pos

```

\sigma_0 := \{x \mapsto neg, y \mapsto pos\}

\sigma_1 := \mathcal{I}[s_1 : x = x \oplus y;] | \sigma_0 = store_{abs} \sigma_0 \ x \ (neg \ xor_{abs} \ pos) = \{x \mapsto neg, y \mapsto pos\}

\sigma_2 := \mathcal{I}[s_2 : y = x \oplus y;] | \sigma_1 = store_{abs} \sigma_1 \ y \ (neg \ xor_{abs} \ pos) = \{x \mapsto neg, y \mapsto neg\}

\sigma_3 := \mathcal{I}[s_3 : x = x \oplus y;] | \sigma_2 = store_{abs} \sigma_2 \ x \ (neg \ xor_{abs} \ neg) = \{x \mapsto \top, y \mapsto neg\}.

```

Fig. 3. Application of the abstract transformers created by the sign-analysis reinterpretation to the initial abstract state  $\sigma_0 = \{x \mapsto neg, y \mapsto pos\}.$

and neg, the high-order bit of the result is set, which means that the result is always negative. However,  $pos\ xor_{abs}\ pos = neg\ xor_{abs}\ neg = \top$  because the concrete result could be either 0 or positive, and  $zero \sqcup pos = \top$ .

For the code fragment shown in Fig. 2, which swaps two ints, sign-analysis reinterpretation creates abstract transformers that, given the initial abstract state  $\sigma_0 = \{x \mapsto neg, y \mapsto pos\}$ , produce the abstract states shown in Fig. 3.  $\square$

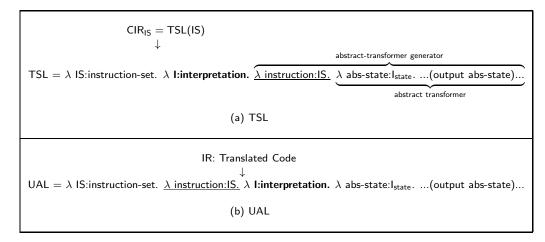

Alternatives to Semantic Reinterpretation. The mapping of a client specification to the operations of the semantic core resembles a translation to a universal assembly language (UAL). Thus, another approach to obtaining "systematic" reinterpretations that are similar to semantic reinterpretations—in that they can be retargeted to multiple subject languages—is to translate subject-language programs to a UAL, and then retarget the instructions of the UAL to operate on abstract values or abstract states. Semantic reinterpretation is compared with this approach in §6.2.

## 2.3 Technical Contributions Incorporated in the TSL Compilation Process

The specific technical contributions incorporated in the part of the TSL compiler that generates the CIR can be summarized as follows:

- —Two-Level Semantics: In the TSL system, the notion of a two-level intermediate language [Nielson and Nielson 1992] is used to generate the CIR in a way that reduces the loss of precision that could otherwise come about with certain reinterpretations. To address this issue, the TSL compiler performs binding-time analysis [Jones et al. 1993] on the TSL specification to identify which values can always be treated as concrete values, and which operations should therefore be performed in the concrete domain (i.e., should not be reinterpreted). §3.2.2 discusses more details of the two-level intermediate language along with binding-time analysis.

- —Abstract Interpretation: From a specification, the TSL compiler generates a CIR that has the ability (i) to execute over abstract states, (ii) possibly propagate abstract states to more than one successor in a conditional expression, (iii) compare abstract states and terminate abstract execution when a fixed point is reached, and (iv) apply widening operators, if necessary, to ensure termination. §3.2.1 contains a detailed discussion of these issues.

- —Paired Semantics: The TSL system allows easy instantiations of reduced products by means of paired semantics. The CIR can be instantiated with a paired semantic domain that couples two interpretations. Communication between the values carried by the two interpretations may take place in the TSL basetype and map-

type operators. §3.2.3 discusses more details of paired semantics.

#### 2.4 The Context of Our Work

TSL has primarily been applied to the creation of abstract interpreters for machine code. Machine-code analysis presents many interesting challenges. For instance, at the machine-code level, memory is one large byte-addressable array, and an analyzer must handle computed—and possibly non-aligned—addresses. It is crucial to track array accesses and updates accurately; however, the task is complicated by the fact that arithmetic and dereferencing operations are both pervasive and inextricably intermingled. For instance, if local variable x is at offset –12 from the activation record's frame pointer (register ebp), an access on x would be turned into an operand [ebp–12]. Evaluating the operand first involves pointer arithmetic ("ebp–12") and then dereferencing the computed address ("[·]"). On the other hand, machine-code analysis also offers new opportunities, in particular, the opportunity to track low-level, platform-specific details, such as memory-layout effects. Programmers are typically unaware of such details; however, they are often the source of exploitable security vulnerabilities.

For more discussion of the challenges and opportunities that arise in machine-code analysis, the reader is referred to [Balakrishnan and Reps 2010] and [Reps et al. 2010]. However, it is worth mentioning a couple of points here that help to illustrate the scope of the problem that TSL addresses:

- —The paper presents several fragments of TSL specifications that specify the operational semantics of instruction sets, such as IA32 (also known as x86) and PowerPC (see §4). In such specifications, the subject language is modeled at the level of the instruction-set semantics. That is, the TSL specification describes how the execution of each instruction changes the execution state. Lower-level hardware operations, such as pipelining and paging, are not modeled in our specifications, although TSL is powerful enough to specify such lower-level operations.

- —Given a TSL specification of an interpreter at the instruction-set level, the TSL compiler generates an analysis component that performs abstract interpretation on a per-instruction basis. It is the tool developer's responsibility to complete the implementation of the analysis by handling the higher levels of abstract interpretation, such as (i) the propagation of abstract values through the control-flow graph, (ii) determining when a fixed point is reached, etc.

To help out in this task, the TSL system provides several kinds of generic execution/analysis engines that can be instantiated to create finished analyses, including (i) a worklist-based solver for abstract-value propagation over a control-flow graph (for static analysis), (ii) an instruction emulator (for dynamic analysis), and (iii) an engine for performing symbolic execution along a path (for symbolic analysis), as well as a solver for aggregate-structure-identification problems (ASI) [Ramalingam et al. 1999; Balakrishnan and Reps 2007]—a unification-based, flow-insensitive algorithm to identify the structure of aggregates in a program.

In addition, we have used TSL-generated abstract transformers with general-purpose analysis packages, such as the WALi system [WALi 2007] for weighted pushdown systems (WPDSs) [Reps et al. 2005; Bouajjani et al. 2003] and the OpenNWA system [Driscoll et al. 2012] for nested-word automata [Alur and

Madhusudan 2006]. In principle, it would be easy to use TSL to drive other similar external packages, such as the Banshee system for solving set-constraint problems [Kodumal and Aiken 2005]. (See §4.1.)

—Although this paper only discusses the application of TSL to machine-code instruction sets, only small extensions would be needed to be able to apply TSL to source-code languages (i.e., to create language-independent analyzers for source-level IRs), as well as bytecode. The main obstacle is that the concrete semantics of a source-code language generally uses an execution state based on a stack of variable-to-value (or variable-to-location, location-to-value) maps. For a machine-code language, the state incorporates an address-based memory model, for which the TSL language provides appropriate primitives.

## 3. TRANSFORMER SPECIFICATION LANGUAGE

This section presents the basic elements of the TSL system. §3.1 describes the basic elements of the TSL language and what is produced by the TSL compiler. It considers the TSL system from the perspective of instruction-set specifiers (ISS), reinterpretation developers, and tool developers. §3.2 discusses how the TSL compiler generates a CIR from a TSL specification and how the CIR is instantiated for creating analysis components. §3.2 also describes how the TSL system handles some important issues, such as recursion and conditional branches in the CIR. §3.3 discusses the leverage that the TSL system provides.

## 3.1 Overview of the TSL Language and its Compilation

The key principle of the TSL system is the separation of the semantics of a subject language from the analysis semantics in the development of an analysis component. As discussed in §2.2, the TSL system is based on semantic reinterpretation, which was originally proposed as a convenient *methodology* for formulating abstract interpretations [Cousot and Cousot 1977; Mycroft and Jones 1985; Jones and Mycroft 1986; Malmkjær 1993; Nielson 1989] (see §2.2). Semantic reinterpretation involves refactoring the specification of the concrete semantics of a language into two parts: (i) a *client* specification, and (ii) a semantic *core*. The client is expressed in terms of the semantic core. Such an organization permits the core to be *reinterpreted* to produce an alternative semantics for the subject language.

The key insight behind the TSL system is that if a rich enough *meta-language* is provided for writing semantic specifications, the meta-language itself can serve as the core, and one thereby obtains a suitable client/core factoring for free.

As presented earlier, the TSL system has three classes of users: (i) instructionset specifiers (ISS), (ii) reinterpretation developers, and (iii) tool developers. The ISS developers use the TSL language to specify the concrete semantics of different instruction sets (the lower part of Fig. 1); the reinterpretation developers use semantic reinterpretation to create new analysis components (the gray boxes in the upper part of Fig. 1).

3.1.1 TSL from an Instruction-Set Specifier's Standpoint. Fig. 4 shows part of a specification of the IA32 instruction set taken from the Intel manual [IA32]. The specification describes the syntax and the semantics of each instruction only in a semi-formal way (i.e., a mixture of English and pseudo-code).

| General Purpose Registers:                                  | ADD r/m32,r32; Add r32 to r/m32            |  |  |  |  |

|-------------------------------------------------------------|--------------------------------------------|--|--|--|--|

| EAX,EBX,ECX,EDX,ESP,EBP,ESI,EDI,EIP                         | ADD r/m16,r16; Add r16 to r/m16            |  |  |  |  |

| Each of these registers also has 16- or 8-bit subset names. | Operation: DEST $\leftarrow$ DEST $+$ SRC; |  |  |  |  |

| Addressing Modes: [sreg:][offset][([base][,index][,scale])] | Flags Affected: The OF,SF,ZF,AF,CF, and    |  |  |  |  |

| EFLAGS register: ZF,SF,OF,CF,AF,PF,                         | PF flags are set according to the result.  |  |  |  |  |

Fig. 4. A part of the Intel manual's specification of IA32's add instruction.

| Type                | Terms                  | Constants                    |

|---------------------|------------------------|------------------------------|

| BOOL                | false, true            | false, true                  |

| INT64               | 64-bit signed integers | 0d64, 1d64, 2d64,            |

| INT32               | 32-bit signed integers | 0d32, 1d32, 2d32,            |

| INT16               | 16-bit signed integers | 0d16, 1d16, 2d16,            |

| INT8                | 8-bit signed integers  | 0d8, 1d8, 2d8,               |

| $MAP[\alpha,\beta]$ | Maps                   | $[\alpha \mapsto v_{\beta}]$ |

Fig. 5. Basetype and map-type constants.  $[\alpha \mapsto v_{\beta}]$  denotes the map  $\lambda x : \alpha \cdot v : \beta$ .

Our work is based on completely formal specifications that are written in TSL's meta language. TSL is a strongly typed, first-order functional language. TSL supports a fixed set of basetypes; a fixed set of arithmetic, bitwise, relational, and logical operators; the ability to define recursive data-types, map-types, and user-defined functions; and a mechanism for deconstruction by means of pattern matching.

Basetypes. Fig. 5 shows the basetypes that TSL provides. There are two categories of primitive basetypes: unparameterized and parameterized. An unparameterized basetype is just a set of terms. For example, BOOL is a type consisting of truth values, INT32 is a type consisting of 32-bit signed whole numbers, etc.  $\mathsf{MAP}[\alpha, \beta]$  is a predefined parameterized type, with parameters  $\alpha$  and  $\beta$ . Each of the following is an instance of the parameterized type MAP:

```

MAP [INT32, INT8]

MAP [INT32, BOOL]

MAP[INT32, MAP[INT8, BOOL]]

```

TSL supports arithmetic/logical operators (+, -, \*, /, !, &&, ||, xor), bitmanipulation operators ( $\sim$ , &, |,  $\hat{}$ ,  $\ll$ ,  $\gg$ , right-rotate, left-rotate), relational operators (<, <=, >, >=, ==, !=), and a conditional-expression operator (?:). TSL also provides access/update operators for map-types.

Specifying an Instruction Set. Fig. 6(a) shows a snippet of the TSL specification that corresponds to Fig. 4. (The TSL specification has been pared down to simplify the presentation.)

Much of what an instruction-set specifier writes in a TSL specification is similar to writing an interpreter for an instruction set in first-order ML. One specifies (i) the abstract-syntax grammar of the instruction-set (e.g., lines 2–9 of Fig. 6(a)), (ii) a type for concrete states (e.g., lines 10-12 of Fig. 6(a)), and (iii) the concrete semantics of each instruction (e.g., lines 14–30 of Fig. 6(a)).

Reserved, but User-Defined Types and Reserved Functions. Each specification must define several reserved (but user-defined) types: in Fig. 6(a), instruction (lines 7–9); state—e.g., for 32-bit Intel x86 the type state is a triple of maps (lines 10–

```

// User-defined abstract syntax

[1] template <class INTERP> class CIR {

reg: EAX() | EBX() | . . . ;

class reg \{\ .\ .\ .\ \};

class EAX : public reg { . . . }; . . .

flag: ZF() | SF() | . . . ;

operand: Indirect(reg reg INT8 INT32)

[4]

class flag \{\ .\ .\ .\ \};

class ZF : public flag \{\ldots\};\ldots

| DirectReg(reg)

[5]

class operand { . . . };

[6]

| Immediate(INT32) | ...;

class Indirect: public operand \{\ .\ .\ .\ \};\ .\ .\ .

[7]

[8]

instruction

: MOV(operand operand)

class instruction { . . . };

class MOV : public instruction {

[9]

| ADD(operand operand|

[10]

operand op1; operand op2; . . .

[10]

state: State(MAP[INT32,INT8]

// memory-map

[11]

MAP[reg32,INT32] // register-map

[12]

class ADD : public instruction \{\ .\ .\ .\ \};\ .\ .

MAP[flag,BOOL]);

// flag-map

class state \{\ .\ .\ .\ \}; class State: public state \{\ .\ .\ .\ \};

[13]

// User-defined functions

[13]

[14]

INT32 interpOp(state S, operand op) { . . . };

\textbf{INTERP::INT32} \ \mathsf{interpOp}(\mathsf{state}\ \mathsf{S},\ \mathsf{operand}\ \mathsf{op})\ \{\ .\ .\ .\ \};

[15]

[15] state updateFlag(state S, . . . ) { . . . };

[16]

state\ updateFlag(state\ S,\ .\ .\ .\ )\ \{\ .\ .\ .\ \};

[16] state updateState(state S, . . . ) { . . . };

state updateState(state S, . . .) { .

[17]

[17]

state \ \underline{interpInstr}(instruction \ I, \ state \ S) \ \{

state interplnstr(instruction I, state S) {

[18]

[18]

with(I) (

switch(I.id) {

[19]

[19]

MOV(dstOp, srcOp):

case ID_MOV:

[20]

[20]

let srcVal = interpOp(S, srcOp);

[21]

case ID_ADD:

[21]

in ( updateState( S, dstOp, srcVal ) ),

operand dstOp = I.get\_child1();

[22]

[22]

ADD(dstOp, srcOp):

[23]

operand srcOp = I.get_child2();

let dstVal = interpOp(S, dstOp);

INTERP::INT32 dstVal = interpOp(S, dstOp);

[24]

[24]

srcVal = interpOp(S, srcOp);

[25]

INTERP::INT32 srcVal = interpOp(S, srcOp);

[25]

res = dstVal + srcVal;

[26]

INTERP::INT32 res = INTERP::Plus(dstVal, srcVal);

[26]

S2 = updateFlag(S, dstVal, srcVal, res);

[27]

state S2 = updateFlag(S, dstVal, srcVal, res);

[27]

in ( updateState( S2, dstOp, res ) ),

ans = updateState( S2, dstOp, res );

break;

[29]

[28]

[30]

[29]

. . }

);

[31] }};

[30] };

(a)

(b)

```

Fig. 6. (a) A part of the TSL specification of IA32 concrete semantics, which corresponds to the specification of add from the IA32 manual. Reserved types and function names are underlined, (b) A part of the CIR generated from (a). The CIR is simplified in this presentation.

12); as well as the reserved TSL function interplastr (lines 17–30). These reserved types and functions form part of the API available to *analysis engines* that use the TSL-generated transformers (i.e., the instantiated CIR).

The definition of types and constructors on lines 2–9 of Fig. 6(a) is an abstract-syntax grammar for IA32. Type reg consists of nullary constructors for the names of the IA32 registers, such as EAX() and EBX(); flag consists of nullary constructors for the names of the IA32 condition codes, such as ZF() and SF(). Lines 4–6 define types and constructors to represent the various kinds of operands that IA32 supports, i.e., various sizes of immediate, direct register, and indirect memory operands. The reserved (but user-defined) type instruction consists of user-defined constructors for each instruction, such as MOV and ADD.

The type state specifies the structure of the execution state. The state for IA32 is defined on lines 10–12 of Fig. 6(a) to consist of three maps, i.e., a memory-map, a register-map, and a flag-map. The *concrete semantics* is specified by writing a function named interplastr (see lines 17–30 of Fig. 6(a)), which maps an instruction and a state to a state. For instance, the semantics of ADD is to evaluate the two operands in the input state S and create a return state in which the target location holds the summation of the two values and the flags hold appropriate flag values.

3.1.2 Case Study of Instruction Sets. In this section, we discuss the quirky characteristics of some instruction sets, and various ways these can be handled in TSL.

IA32. To provide compatibility with 16-bit and 8-bit versions of the instruction set, IA32 provides overlapping register names, such as AX (the lower 16-bits of EAX), AL (the lower 8-bits of AX), and AH (the upper 8-bits of AX). There are two possible ways to specify this feature in TSL. One is to keep three separate maps, for 32-bit registers, 16-bit registers, and 8-bit registers, respectively, and specify that updates to any one of the maps affect the other two maps. Another is to keep one 32-bit map for registers, and obtain the value of a 16-bit or 8-bit register by masking the value of the 32-bit register. (The former can yield more precise VSA results.) Similarly, a 32-bit register is updated with the value of the corresponding 16-bit or 8-bit register by masking and performing a bitwise-or.

The IA32 instruction set keeps condition codes in a special register, called EFLAGS. (Many other instruction sets, such as SPARC, PowerPC, and ARM, also use a special register to store condition codes.) One way to address this feature is to declare "reg32: Eflags();", and make every flag manipulation fetch the bit value from an appropriate bit position of the value associated with Eflags in the register-map. Another way is to introduce flag names, as in our examples, and have every manipulation of EFLAGS affect the entries in a flag-map for the individual flags.

ARM. Almost all ARM instructions contain a condition field that allows an instruction to be executed conditionally, depending on condition-code flags. This feature reduces branch overhead and compensates for the lack of a branch predictor. However, it may worsen the precision of an abstract analysis because in most instructions' specifications, the abstract values from two arms of a TSL conditional expression would be joined.

```

MOVEQ(destReg, srcOprnd):

let cond = flagMap(EQ());

src = interpOperand(curState, srcOprnd);

a = regMap[destReg |-> src];

b = regMap;

answer = cond ? a: b;

in (answer)

```

Fig. 7. An example of the specification of an ARM conditional-move instruction in TSL.

For example, MOVEQ is one of ARM's conditional instructions; if the flag EQ is true when the instruction starts executing, it executes normally; otherwise, the instruction does nothing. Fig. 7 shows the specification of the instruction in TSL. In many abstract semantics, the conditional expression "cond? a:b" will be interpreted as a join of the original register map b and the updated map a, i.e., join(a,b). Consequently, destReg would receive the join of its original value and src, even when cond is known to have a definite value (TRUE or FALSE) in VSA semantics. The paired-semantics mechanism presented in §3.2.3 can help with improving the precision of analyzers by abstractly interpreting conditions. When the

```

\begin{array}{lll} [1] & \mathsf{reg32} : \mathsf{Reg}(\mathsf{INT8}) \mid \mathsf{CWP}() \mid \ldots; \\ [2] & \mathsf{reg32} : \mathsf{OutReg}(\mathsf{INT8}) \mid \mathsf{InReg}(\mathsf{INT8}) \mid \ldots; \\ [3] & \mathsf{state} : \mathsf{State}(\ \ldots\ , \mathsf{MAP}[\mathsf{var32},\mathsf{INT32}], \ldots\ ); \\ [4] & \mathsf{INT32} & \mathsf{RegAccess}(\mathsf{MAP}[\mathsf{var32},\mathsf{INT32}] \ \mathsf{regmap}, \ \mathsf{reg32} \ \mathsf{r}) \ \{ \\ [5] & \mathsf{let} & \mathsf{cwp} = \mathsf{regmap}(\mathsf{CWP}()); \\ [6] & \mathsf{key} = \mathsf{with}(\mathsf{r}) \ ( \\ [7] & \mathsf{OutReg}(i): \\ [8] & \mathsf{Reg}(8+i+(16+\mathsf{cwp*16})\%(\mathsf{NWINDOWS*16}), \\ [9] & \mathsf{InReg}(i): \ \mathsf{Reg}(8+i+\mathsf{cwp*16}), \\ [10] & \ldots\ ); \\ [11] & \mathsf{in} \ ( \ \mathsf{regmap}(\mathsf{key}) \ ) \\ [12] \} \end{array}

```

Fig. 8. A method to handle the SPARC register window in TSL.

CIR is instantiated with a paired semantics of VSA\_INTERP and DUA\_INTERP, and the VSA value of *cond* is FALSE, the DUA\_INTERP value for *answer* gets empty *def*-and *use*-sets because the true branch *a* is known to be unreachable according to the VSA\_INTERP value of *cond* (instead of non-empty sets for *def*s and *use*s that contain all the definitions and uses in *destReg* and *srcOprnd*).

SPARC. SPARC uses register windows to reduce the overhead associated with saving registers to the stack during a conventional function call. Each window has 8 in, 8 out, 8 local, and 8 global registers. Outs become ins on a context switch, and the new context gets a new set of out and local registers. A specific platform will have some total number of registers, which are organized as a circular buffer; when the buffer becomes full, registers are spilled to the stack to free up a sufficient number for the called procedure. Fig. 8 shows a way to accommodate this feature. The syntactic register (OutReg(n) or InReg(n), defined on line 2) in an instruction is used to obtain a semantic register (Reg(m), defined on line 1, where m represents the register's global index), which is the key used for accesses on and updates to the register map. The desired index of the semantic register is computed from the index of the syntactic register, the value of CWP (the current window pointer) from the current state, and the platform-specific value NWINDOWS (lines 8–9).

3.1.3 Common Intermediate Representation (CIR). Fig. 6(b) shows part of the common intermediate representation (CIR) generated by the TSL compiler from Fig. 6(a). (The CIR has been simplified for the presentation in the paper.)

The CIR generated for a given TSL specification is a C++ template that can be used to create multiple analysis components by instantiating the template with different semantic reinterpretations. Each generated CIR is *specific* to a given instruction-set specification, but *common* (whence the name CIR) across generated analyses. Each generated CIR is a template class that takes as input class INTERP, which is an abstract domain for an analysis (line 1 of Fig. 6(b)). The user-defined abstract syntax (lines 2–9 of Fig. 6(a)) is translated to a set of C++ abstract-syntax classes (lines 2–12 of Fig. 6(b)). The user-defined types, such as reg, operand, and instruction, are translated to abstract C++ classes, and the constructors, such as EAX(), Indirect(\_,\_,\_,), and ADD(\_,\_,), are subclasses of the appropriate parent abstract C++ classes.

Each user-defined function is translated to a CIR function (lines 15–31 of

Fig. 6(b)). Each TSL basetype and basetype-operator is pre-pended with the template parameter name INTERP. To instantiate the CIR, class INTERP is supplied by an analysis developer for the analysis of interest.

The TSL front-end performs with-normalization, which transforms all multi-level with expressions to use only one-level patterns, and then compiles the one-level pattern via the pattern-compilation algorithm developed by Wadler [1987] and Pettersson [1992]. Thus, the with expression on line 18 and the patterns on lines 19 and 22 of Fig. 6(a) are translated into switch statements in C++ (lines 19–30 in Fig. 6(b)).

The function calls for obtaining the values of the two operands (lines 23–24 in Fig. 6(a)) correspond to the C++ code on lines 22–25 in Fig. 6(b). The TSL basetype-operator + on line 25 in Fig. 6(a) is translated into a call to INTERP::Plus, as shown on line 26 in Fig. 6(b). The function calls for updating the state (lines 26–27 in Fig. 6(a)) are translated into C++ calls (lines 27–28 in Fig. 6(b)).

§3.2 presents more details about how the CIR is generated and what kind of facilities CIR provides for creating analysis components.

3.1.4 TSL from a Reinterpretation Developer's Standpoint. A reinterpretation developer creates a new analysis component by (i) redefining (in C++) the TSL basetypes (BOOL, INT32, INT8, etc.), and (ii) redefining (in C++) the primitive operations on basetypes ( $+_{\text{INT32}}$ ,  $+_{\text{INT8}}$ , etc.). These are used to instantiate the CIR template by passing a class of basetypes as the template parameter. This approach implicitly defines an alternative interpretation of each expression and function in an instruction-set's concrete semantics (including interplnstr), and thereby yields an alternative semantics for an instruction set from its concrete semantics.

Table I. Parts of the declarations of the basetypes, basetype-operators, and map-access/update functions for three analyses.

```

DUA

OFBV

[1] class VSA_INTERP {

[1] class DUA_INTERP {

[1] class QFBV_INTERP {

// basetype

// basetype

// basetype

[2]

typedef ValueSet32 INT32;

typedef UseSet INT32;

typedef QFBVTerm32 INT32;

[3]

[3]

[3]

[4]

// basetype-operators

// basetype-operators

// basetype-operators

INT32 Plus(INT32 a, INT32 b)

[6]

INT32 Plus(INT32 a, INT32 b)

INT32 Plus(INT32 a, INT32 b) {

[7]

return a.addValueSet(b);

return a.Union(b);

return QFBVPlus32(a, b);

[8]

[8]

}

[8]

}

[9]

[9]

[9]

[10] // map-basetypes

// map-basetypes

[10]

[10]

// map-basetypes

[11] typedef Map<reg32,INT32>

typedef Map<var32,INT32>

typedef QFBVArrav

[11]

[11]

REGMAP32

REGMAP32;

REGMAP32

[12]

[12]

[13]

[13]

[13]

// map-access/update functions

// map-access/update functions

// map-access/update functions

[15] INT32 MapAccess(

[15]

INT32 MapAccess(

[15]

INT32 MapAccess(

REGMAP32 m, reg32 k)

REGMAP32 m, reg32 k) {

REGMAP32 m, reg32 k) {

[16]

return QFBVArrayAccess(m,k);

return m.Lookup(k);

[17]

return m.Lookup(k);

[17]

[18]

[18]

[19] REGMAP32

[19] REGMAP32

[19] REGMAP32

[20] MapUpdate( REGMAP32 m.

[20] MapUpdate( REGMAP32 m,

[20] MapUpdate( REGMAP32 m,

reg32 k, INT32 v) {

[21]

reg32 k, INT32 v) {

[21]

reg32 k, INT32 v) {

[22]

return m.Insert(k, v);

[22]

[22]

return QFBVArrayUpdate(m,k,v);

return m.Insert(k,v);

[23] }

[23] }

[23] }

[24]

[25]}:

[25]}:

```

Tab. I shows the implementations of primitives for three selected analyses: value-

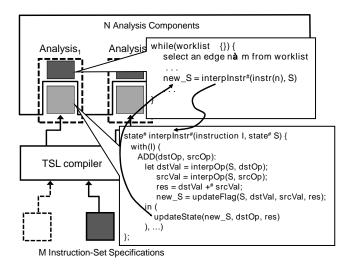

Fig. 9. How a TSL-generated abstract interpreter for instructions, interplnstr<sup>‡</sup>, is invoked by an analysis engine that performs classical worklist-based propagation of abstract states.

set analysis (VSA, see §4.1.1), def-use analysis (DUA, see §4.1.4), and quantifier-free bit-vector semantics (QFBV, see §4.1.5). Each interpretation defines an abstract domain. For example, line 3 of each column defines the abstract-domain class for INT32: ValueSet32, UseSet, and QFBVTerm32, respectively. To define an interpretation, one needs to define 42 basetype operators, most of which have four variants, for 8-, 16-, 32-, and 64-bit integers, as well as 12 map access/update operations. Each abstract domain is also required to contain a set of reserved functions, such as join, meet, and widen, which forms an additional part of the API available to analysis engines that use TSL-generated transformers (see §4).

Usage of TSL-Generated Analysis Components. Fig. 9 shows how the CIR is connected to an analysis engine. The analysis engine in Fig. 9 uses classical worklist-based value propagation in which the TSL-generated transformer interplastr is invoked with an instruction and the current state S. On each iteration of the main loop of the solver, changes (new\_S) would be propagated to successors/predecessors (depending on propagation direction). §4.1 discusses more about how different kinds of analysis engines make use of the CIR.

Generated Transformers. Consider the instruction "add ebx, eax", which causes the sum of the values of the 32-bit registers ebx and eax to be assigned into ebx. When Fig. 6(b) is instantiated with the three interpretations from Tab. I, lines 17–30 of Fig. 6(a) implement the three transformers that are presented (using mathematical notation) in Tab. II.

## 3.2 More About the Common Intermediate Representation

Given a TSL specification of an instruction set, the TSL system generates a CIR that consists of two parts: one is a list of C++ classes for the user-defined abstract-syntax grammar; the other is a list of C++ template functions for the user-defined

Table II. Semantics of the abstract transformers created using the TSL system.

| Analysis | Generated Transformers for "add ebx, eax"                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1.VSA    | $\lambda S.S[ebx \mapsto S(ebx) + {}^{vsa}S(eax)] [ZF \mapsto (S(ebx) + {}^{vsa}S(eax) = 0)][more\ flag\ updates]$                      |

| 2.DUA    | $[ebx \mapsto \{eax, ebx\}, ZF \mapsto \{eax, ebx\}, \dots]$                                                                            |

| 3.QFBV   | $(ebx' = ebx + ^{32}eax) \land (ZF' \Leftrightarrow (ebx + ^{32}eax = 0)) \land (SF' \Leftrightarrow (ebx + ^{32}eax < 0)) \land \dots$ |

```

[1] INTERP::BOOL t0 = ...; // translation of a

INTERP::INT32 t1, t2, answer;

if(Bool3::possibly_true(t0.getBool3Value())) {

[4]

[5]

t1=\ldots ; // translation of a

[6]

\mathsf{answer} = \mathsf{t1};

[7]

[8]

if(Bool3::possibly_false(t0.getBool3Value())) {

[9]

[10]

t2 = \dots; // translation of b

[11]

\mathsf{answer} = \mathsf{t2};

[12] }

[13] if(t0.getBool3Value() == Bool3::MAYBE) {

answer = t1.join(t2);

[15] }

```

Fig. 10. The translation of the conditional expression "let answer = cond? a: b".

functions, including the interface function interplastr. The C++ functions are generated by linearizing the TSL specification, in evaluation order, into a series of C++ statements, as illustrated by Fig. 6(b). However, there are several issues—discussed below—that need to be properly handled for the resulting code to be suitable for abstract interpretation via semantic reinterpretation.

- —§3.2.1 concerns the basic properties needed so that the code can be executed over an abstract domain.

- —§3.2.2 discusses a technique that is needed with some generated abstract transformers to side-step a loss of precision during abstract interpretation that would otherwise occur.

- —§3.2.3 presents the paired-semantics facility that the TSL system provides.

- 3.2.1 Execution over an Abstract Domain. There are four basic properties that the CIR code must support so that it can be executed over an abstract domain. In particular, the code generated for each transformer must be able to

- (1) execute over abstract values and abstract states,

- (2) possibly propagate abstract values to more than one successor in a conditional expression,

- (3) compare abstract states and terminate abstract execution when a fixed point is reached, and

- (4) apply widening operators, if necessary, to ensure termination.

Conditional Expressions. Fig. 10 shows part of the CIR that corresponds to the TSL expression "let answer = cond? a: b". Bool3 is an abstract domain of Booleans

```

[1] state repMovsd(state S, INT32 count) {

[1] state global_S;

[2]

count == 0

[2] INTERP::INT32 global_count;

state global_retval;

[3]

? S

[4] state repMovsd(

[4]

: with(S) (

Istate S, INTERP::INT32 count) {

[5]

[5]

State(mem, regs, flags):

global_S = \bot;

[6]

let direction = flags(DF());

[6]

global_count = \bot;

[7]

[7]

edi = regs(EDI());

[8]

global retval = 1:

esi = regs(ESI());

[8]

[9]

return repMovsdAux(S, count);

src = MemAccess_32_8_LE_32(mem, esi);

[9]

[10] }:

[10]

newRegs = direction

[11]state repMovsdAux(

[11]

? regs[EDI()|->edi-4][ESI()|->esi-4]

state S, INTERP::INT32 count) {

[12]

: regs[EDI()|->edi+4][ESI()|->esi+4]

[13]

// Widen and test for convergence

[13]

newMem = MemUpdate_32_8_LE_32(

state tmp_S = global_S \nabla (global_S \sqcup S);

[14]

INTERP::INT32 tmp_count =

[14]

memory, edi, src);

[15]

[15]

newS = State(newMem, newRegs, flags);

[16]

\mathsf{if}(\mathsf{tmp\_S} \sqsubseteq \mathsf{global\_S}

[17]

[16]

in ( repMovsd(newS, count - 1) )

[18]

&& tmp_count \sqsubseteq global_count) {

[17]

[19]

return global_retval;

[18]};

[20]

[21]

S = tmp\_S; global\_S = tmp\_S;

[22]

count = tmp_count; global_count = tmp_count;

[23]

// translation of the body of repMovsd

[24]

[25]

[26]

state newS = .

[27]

state t = repMovsdAux(newS, count - 1);

global\_retval = global\_retval \sqcup t;

return global_retval;

[29]

[30]}:

(a)

(b)

```

Fig. 11. (a) A recursive TSL function, (b) The translation of the recursive function from (a). For simplicity, some mathematical notation is used, including  $\sqcup$  (join),  $\nabla$  (widening),  $\sqsubseteq$  (approximation), and  $\bot$  (bottom).

(which consists of three values {TRUE, FALSE, MAYBE}, where MAYBE means "may be TRUE or may be FALSE"). The TSL conditional expression is translated into three if-statements (lines 3–7, lines 8–12, and lines 13–15 in Fig. 10). The body of the first if-statement is executed when the Bool3 value for cond is possibly true (i.e., either TRUE or MAYBE). Likewise, the body of the second if-statement is executed when the Bool3 value for cond is possibly false (i.e., either FALSE or MAYBE). The body of the third if-statement is executed when the Bool3 value for cond is MAYBE. Note that in the body of the third if-statement, answer is overwritten with the *join* of t1 and t2 (line 14).

The Bool3 value for the translation of a TSL BOOL-valued value is fetched by getBool3Value, which is one of the TSL interface functions that each interpretation is required to define for the type BOOL. Each analysis developer decides how to handle conditional branches by defining getBool3Value. It is always sound for getBool3Value to be defined as the constant function that always returns MAYBE. For instance, this constant function is useful when Boolean values cannot be expressed in an abstract domain, such as DUA for which the abstract domain for BOOL is a set of uses. For an analysis where Bool3 is itself the abstract domain for type BOOL, such as VSA, getBool3Value returns the Bool3 value from evaluating the translation of a so that either an appropriate branch or both branches can be abstractly executed.

Comparison, Termination, and Widening. Recursion is not often used in TSL specifications, but is needed for handling some instructions that involve iteration, such as the IA32 string-manipulation instructions (STOS, LODS, MOVS, etc., with various REP prefixes), and the PowerPC multiple-word load/store instructions (LMW, STMW, etc). For these instructions, the amount of work performed is controlled either by the value of a register, the value of one or more strings, etc. These instructions can be specified in TSL using recursion. For each recursive function, the TSL system generates a function that appropriately compares abstract values and terminates the recursion if abstract values are found to be equal (i.e., the recursion has reached a fixed point). The function is also prepared to apply the widening operator that the reinterpretation developer has specified for the abstract domain in use.

For example, Fig. 11(a) shows the user-defined TSL function that handles "rep movsd", which copies the contents of one area of memory to a second area.<sup>5</sup> The amount of memory to be copied is passed into the function as the argument count. Fig. 11(b) shows its translation in the CIR. A recursive function like repMovsd (Fig. 11(a)) is automatically split by the TSL compiler into two functions, repMovsd (line 4 of Fig. 11(b)) and repMovsdAux (line 11 of Fig. 11(b)). The TSL system initializes appropriate global variables global\_S and global\_count (lines 6–8) in repMovsd, and then calls repMovsdAux (line 9). At the beginning of repMovsdAux, it generates statements that widen each of the global variables with respect to the arguments, and test whether all of the global variables have reached a fixpoint (lines 13–17). If so, repMovsdAux returns global\_retval (line 19). If not, the body of repMovsdAux is analyzed again (lines 24–27). Note that at the translation of each normal return from repMovsdAux (e.g., line 28), the return value is joined into global\_retval. The TSL system requires each reinterpretation developer to define the functions join and widen for the basetypes of the interpretation used in the analysis.

3.2.2 Two-Level CIR. The examples given in Fig. 6(b), Fig. 10, and Fig. 11(b), show slightly simplified versions of CIR code. The TSL system actually generates CIR code in which all the basetypes, basetype-operators, and access/update functions are appended with one of two predefined namespaces that define a two-level interpretation [Jones and Nielson 1995; Nielson and Nielson 1992]: CONCINTERP for concrete interpretation (i.e., interpretation in the concrete semantics), and AB-SINTERP for abstract interpretation. Either CONCINTERP or ABSINTERP would replace the occurrences of INTERP in the example CIR shown in Fig. 6(b), Fig. 10, and Fig. 11(b).

The reason for using a two-level CIR is that the specification of an instruction set often contains some manipulations of values that should always be treated as concrete values. For example, an instruction-set specification developer could follow the approach taken in the PowerPC manual [PowerPC32] and specify variants of the conditional branch instruction (BC, BCA, BCL, BCLA) of PowerPC by interpreting some of the fields in the instruction (AA and LK) to determine which of the four variants is being executed (Fig. 12).

Another reason that this issue arises is that most well-designed instruction sets

$<sup>^4\</sup>mathrm{Currently},\,\mathsf{TSL}$  supports only linear tail-recursion.

$<sup>^{5}</sup>$ repMovsd is called by interplastr, which passes in the value of register ecx, and sets ecx to 0 after

```

[1] // User-defined abstract-syntax grammar

[2] instruction: .

| BCx(BOOL BOOL INT32 BOOL BOOL)

[3]

[5] // User-defined functions

[6] state interplnstr(instruction I, state S) {

[7]

BCx(BO, BI, target, AA, LK):

[8]

[9]

[10]

cia = RegValue32(S, CIA()); // current address

// direct: BCA/BCLA

[11]

new_ia = (AA ? target

[12]

: cia + target); // relative: BC/BCL

Ir = RegValue32(S, LR()); // linkage address

[13]

[14]

(LK ? cia + 4 // change the link register: BCL/BCLA

[15]

[16]

: Ir); // do not change the link register: BC/BCA

[17]

[18]}

```

Fig. 12. A fragment of the PowerPC specification for interpreting BCx instructions (BC, BCA, BCL, BCLA). For a given instruction, each of BO, BI, target, AA, and LK will have a specific concrete value.

```

AddSubInstr(op, dstOp, srcOp): // ADD or SUB

let dstVal = interpOp(S, dstOp);

srcVal = interpOp(S, srcOp);

ans = (op == ADD() ? dstVal + srcVal

dstVal - srcVal); // SUB()

in ( . . . ),

. . .

```

Fig. 13. An example of factoring in TSL.

have many regularities, and it is convenient to factor the TSL specification to take advantage of these regularities when specifying the semantics. Such factoring leads to shorter specifications, but leads to the introduction of auxiliary functions in which one of the parameters holds a constant value for a *given* instruction. Fig. 13 shows an example of factoring. The IA32 instructions add and sub both have two operands and can share the code for fetching the values of the two operands. Lines 4–5 are the instruction-specific operations; the equality expression "op == ADD()" on line 4 can be (and should be) interpreted in concrete semantics.

In both cases, the precision of an abstract transformer can sometimes be improved—and is never made worse—by interpreting subexpressions associated with the manipulation of concrete values in concrete semantics. For instance, consider a TSL expression  $let\ v=(b\ ?\ 1:2)$  that occurs in a context in which b is definitely a concrete value; v will get a precise value—either 1 or 2—when b is concretely interpreted. However, if b is not expressible precisely in a given abstract domain, the conditional expression " $(b\ ?\ 1:2)$ " will be evaluated by joining the two branches, and v will not hold a precise value. (It will hold the abstraction of  $\{1,2\}$ .)

$repMovsd\ returns.$

```

template <typename INTERP1, typename INTERP2>

class PairedSemantics {

[2]

typedef PairedBaseType<INTERP1::INT32, INTERP2::INT32> INT32;

[3]

[5]

INT32 MemAccess_32_8_LE_32(MEMMAP32_8 mem, INT32 addr) {

[6]

return INT32(INTERP1::MemAccess_32_8_LE_32(mem.GetFirst(), addr.GetFirst()),

INTERP2::MemAccess_32_8_LE_32(mem.GetSecond(), addr.GetSecond()));

[7]

[8]

[9]

typedef PairedSemantics<VSA_INTERP, DUA_INTERP> DUA;

[1]

template<> DUA::INT32 DUA::MemAccess_32_8_LE_32(

[2]

DUA::MEMMAP32_8 mem, DUA::INT32 addr) {

[4]

DUA::INTERP1::MEMMAP32_8 memory1 = mem.GetFirst();

\mathsf{DUA} :: \mathsf{INTERP2} :: \mathsf{MEMMAP32\_8} \ \mathsf{memory2} = \mathsf{mem.GetSecond}();

[6]

DUA::INTERP1::INT32 addr1 = addr.GetFirst();

DUA::INTERP2::INT32 addr2 = addr.GetSecond()

DUA::INT32 answer = interact(mem1, mem2, addr1, addr2);

[9]

return answer;

```

Fig. 14. (a) A part of the template class for paired semantics; (b) an example of C++ explicit template specialization to create a reduced product.

Binding-time analysis. To address the issue, we perform a kind of binding-time analysis [Jones et al. 1993] on the TSL code, the outcome of which is that expressions associated with the manipulation of concrete values in an instruction are annotated with C, and others with A. We then generate the two-level CIR by appending CONCINTERP for C values, and ABSINTERP for A values. The generated CIR is instantiated for an analysis transformer by defining ABSINTERP. The TSL translator supplies a predefined concrete interpretation for CONCINTERP.

The instruction-set-specification developer annotates the top-level user-defined (but reserved) functions, including interplastr, with binding-time information.

$$\mathsf{EXPORT} < A > \mathsf{interpInstr}(< C >, < A >)$$

The first argument of interplnstr, of type instruction, is annotated with  $<\!C\!>$ , which indicates that all data extracted from an instruction is treated as *concrete*. The second argument of interplnstr, of type state, is annotated with  $<\!A\!>$ , which indicates that all data extracted from state is treated as *abstract*. The return type is also annotated as  $<\!A\!>$ .

Binding-time information is propagated through a TSL specification until a fixed point is reached, or an inconsistency is identified.

3.2.3 Paired Semantics. Our system allows easy instantiations of reduced products [Cousot and Cousot 1979] by means of paired semantics. The TSL system provides a template for paired semantics as shown in Fig. 14(a).

The CIR is instantiated with a paired semantic domain defined with two interpretations, INTERP1 and INTERP2 (each of which may itself be a paired semantic domain), as shown on line 1 of Fig. 14(b). The communication between interpretations may take place in basetype-operators or access/update functions; Fig. 14(b) is an example of the latter. The two components of the paired-semantics values are deconstructed on lines 4–7 of Fig. 14(b), and the individual INTERP1 and INTERP2 components from both inputs can be used (as illustrated by the call to interact on line 8 of Fig. 14(b)) to create the paired-semantics return value, answer. Such overridings of basetype-operators and access/update functions are done by C++

```

[1] with(op) ( . . .

[2] Indirect32(base, index, scale, disp):

[3] let addr = base

[4] + index * SignExtend8To32(scale)

[5] + disp;

[6] m = MemUpdate_32_8_LE_32(

[7] mem,addr,v);

[8] . . .)

```

Fig. 15. A fragment of updateState.

explicit specialization of members of class templates (this is specified in C++ by "template<>"; see line 2 of Fig. 14(b)).

We also found this method of CIR instantiation to be useful to perform a form of reduced product when analyses are split into multiple phases, as in a tool like CodeSurfer/x86. CodeSurfer/x86 carries out many analysis phases, and the application of its sequence of basic analysis phases is itself iterated. On each round, CodeSurfer/x86 applies a sequence of analyses: VSA, DUA, and several others. VSA is the primary workhorse, and it is often desirable for the information acquired by VSA to influence the outcomes of other analysis phases by pairing the VSA interpretation with another interpretation.

We can use the paired-semantics mechanism to obtain desired multi-phase interactions among our generated analyzers—typically, by pairing the VSA interpretation with another interpretation. For instance, with DUA\_INTERP alone, the information required to obtain abstract memory location(s) for addr is lost because the DUA basetype-operators (used for + and \* on lines 4–5 of Fig. 15) just return the union of the arguments' use sets. With the pairing of VSA\_INTERP with DUA\_INTERP (line 1 of Fig. 14(b)), DUA can use the abstract address computed for addr2 (line 7 of Fig. 14(b)) by VSA\_INTERP, which uses VSA\_INTERP::Plus and VSA\_INTERP::Times; the latter operators operate on a numeric abstract domain (rather than a set-based one).

Note that during the application of the paired semantics, VSA interpretation will be carried out on the VSA component of paired intermediate values. In some sense, this is duplicated work; however, a paired semantics is typically used only in a phase of transformer generation where the transformers are generated during a single pass over the interprocedural CFG to generate a transformer for each instruction. Thus, only a limited amount of VSA evaluation is performed (equal to what would be performed to check that the VSA solution is a fixed point).

# 3.3 Leverage

The TSL system provides two dimensions of parameterizability: different instruction sets and different analyses. Each instruction-set specification developer writes an instruction-set semantics, and each reinterpretation developer defines an abstract domain for a desired analysis by giving an interpretation (i.e., the implementations of TSL basetypes, basetype-operators, and <code>access/update</code> functions). Given the inputs from these two classes of users, the TSL system automatically generates an analysis component. Note that the work that an analysis developer performs is TSL-specific but <code>independent</code> of each language to be analyzed; from the interpretation that defines an analysis, the abstract transformers for that analysis can be

generated automatically for every instruction set for which one has a TSL specification. Thus, to create  $M \times N$  analysis components, the TSL system only requires M specifications of the concrete semantics of instruction sets, and N analysis implementations (Fig. 1), i.e., M+N inputs to obtain  $M\times N$  analysis-component implementations.

The TSL system provides considerable leverage for implementing analysis tools and experimenting with new ones. New analyses are easily implemented because a clean interface is provided for defining an interpretation.

TSL as a Tool Generator. A tool generator (or tool-component generator) such as YACC [Johnson 1975] takes a declarative description of some desired behavior and automatically generates an implementation of a component that behaves in the desired way. Often the generated component consists of generated tables and code, plus some unchanging driver code that is used in each generated tool component. The advantage of a tool generator is that it creates correct-by-construction implementations.

For machine-code analysis, the desired components each consist of a suitable abstract interpretation of the instruction set, together with some kind of analysis driver (a solver for finding the fixed-point of a set of dataflow equations, a symbolic evaluator for performing symbolic execution, etc.). TSL is a system that takes a description of the concrete semantics of an instruction set, a description of an abstract interpretation, and creates an implementation of an abstract interpreter for the given instruction set.

$\mathsf{TSL}$ : concrete semantics  $\times$  abstract domain  $\to$  abstract semantics.

In that sense, TSL is a tool generator that, for a fixed instruction-set semantics, automatically creates different abstract interpreters for the instruction set.

The reinterpretation mechanism allows TSL to be used to implement tool-component generators and tool generators. Each implementation of an analysis component's driver (e.g., fixed-point-finding solver, symbolic executor) serves as the unchanging driver for use in different instantiations of the analysis component for different instruction sets. The TSL language becomes the specification language for retargeting that analysis component for different instruction sets:

analyzer generator = abstract-semantics generator + analysis driver.

For tools like CodeSurfer/x86, which incorporates multiple analysis components, we thereby obtain YACC-like tool generators for such tools:

concrete semantics of L  $\rightarrow$  Tool/L.

Consistency. In addition to leverage and thoroughness, for a system like CodeSurfer/x86—which uses multiple analysis phases—automating the process of creating abstract transformers ensures semantic consistency; that is, because analysis implementations are generated from a single specification of the instruction set's concrete semantics, this guarantees that a consistent view of the concrete semantics is adopted by all of the analyses used in the system.

## 4. APPLICATIONS

The capabilities of the TSL system have been demonstrated by writing specifications for both the IA32 and PowerPC instruction sets, and then automatically cre-

ating a variety of abstract interpreters from each of the specifications—including dynamic-analysis components, static-analysis components, and symbolic-analysis components.

In this section, we present various abstract interpreters generated using TSL, as well as summarize various program-analysis tools developed by using the TSL-generated abstract interpreters.

## 4.1 TSL-Generated Abstract Interpreters

As illustrated in Fig. 9, a version of the interface function interplastr is created for each reinterpretation supplied by a reinterpretation designer. At appropriate moments, each analysis engine calls interplastr with an instruction being processed either (i) to perform one step of abstract interpretation, or (ii) to obtain an abstract transformer. Analysis engines can be categorized as follows:

- Worklist-based value propagation (or Transformer application) [TA]. These perform classical worklist-based value propagation in which generated transformers are applied, and changes are propagated to successors/predecessors (depending on propagation direction). Context sensitivity in such analyses is supported by means of the call-string approach [Sharir and Pnueli 1981]. VSA uses this kind of analysis engine (§4.1.1).

- Transformer composition [TC]. These generally perform flow-sensitive, context-sensitive interprocedural analysis. ARA (§4.1.2) uses this kind of analysis engine.

- —Unification-based analyses [UB]. These perform flow-insensitive interprocedural analysis. ASI (§4.1.3) uses this kind of analysis engine.